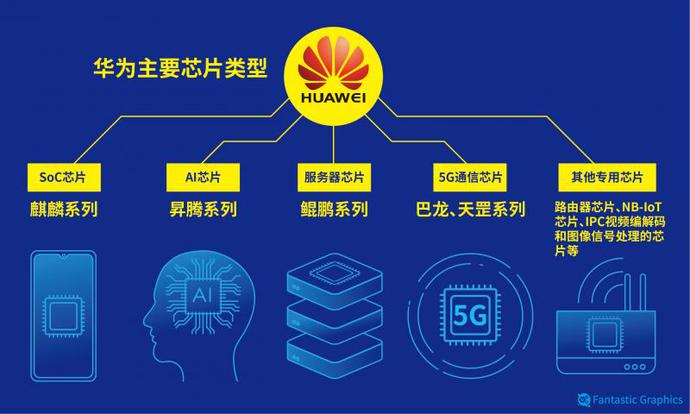

從二級部門獨立,海思正式“轉正”

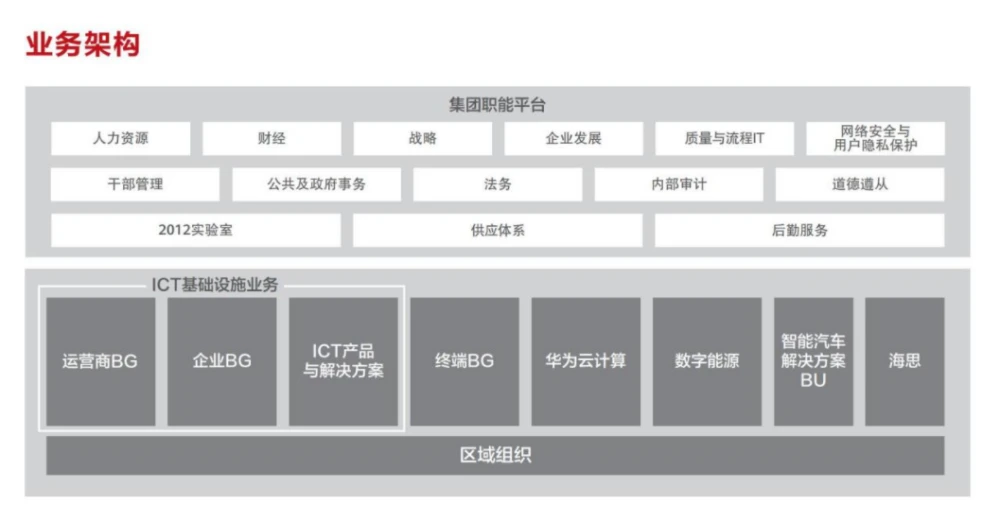

成立于2004年10月的海思,全名是華為海思半導體有限公司,前身是創建于1991年的華為集成電路設計中心,華為多年來能夠在眾多設備用上自研芯片,離不開海思,其是華為的芯片研發設計部門。

自成立以來,海思創下了多個自主化國產系列芯片產品,覆蓋華為各項業務,其中大家所熟知的華為手機芯片麒麟系列就出自海思。此外,華為海思發布的巴龍5000芯片,是全球首款支持5G NSA/SA網絡的通信基帶,而990 5G是全球首款內置5G基帶的芯片,發布上市時間要比高通早半年之久。

除了自研的手機和基帶芯片,海思的產品還有鯤鵬系列的服務器芯片、基站芯片、AI芯片、視頻芯片等。

在華為公布的2021年度報告中可以看出,海思定位于面向智能終端、顯示面板、家電、汽車電子等行業提供感知、聯接、計算、顯示等端到端的板級芯片和模組解決方案,承擔芯片和模組產業的研發、Marketing、生態發展、銷售服務等職責,對經營結果、風險、市場競爭力和客戶滿意度負責。

不過,華為海思僅研發設計芯片,并不生產制造芯片。余承東也曾表示,之前只注重了設計,沒有在制造方面下功夫,在臺積電收到禁令不能出貨給海思之后,海思的高端芯片代工渠道被一刀切斷,其研發設計的很多芯片徹底無法生產制造。

在受到制裁之前,華為海思還一度成為了全球第十大半導體芯片企業。根據 DIGITIMES Research 發布的2018年全球前十大無晶圓廠IC設計公司(Fabless)排名,海思以75億美元營收排名全球第五。

而在華為受到美國制裁之后,因為消費者業務的大幅下滑,海思的處境也不容樂觀。根據市場調研機構 Strategy Analytics 去年公布的報告顯示,雖然2021年一季度5G基帶的出貨量同比增長了三倍,但在主流的第一梯隊中,市場份額占比排名靠前的分別為:高通、聯發科、三星LSI、英特爾以及紫光展銳,華為海思的麒麟芯片跌出了前五。

在這樣的困境和頹勢之下,華為卻宣布全面進入芯片半導體領域,近年來,華為旗下的哈勃投資已經投資了國內多家半導體企業,而這些芯片企業也正在成為華為的“芯片備胎大軍”,目的就是盡快聯合國內芯片產業鏈一起實現突破,從而打破只能設計一流芯片,卻不能生產的局面。

關于海思備胎的定位,任正非曾經在2019年接受采訪時表示,備胎就是正胎壞了才用,以前以正胎為主,現在以備胎為主。他認為,備胎的意義就是為了保證汽車拋錨的時候還能開。當年,主管華為芯片業務的負責人何庭波也在內部信中表示,“華為曾經打造的備胎,一夜之間全部轉正!多年心血,在一夜之間兌現為公司對于客戶持續服務的承諾。”

去年,華為的研發投入再創新高,達到了1427億元人民幣,十年累計投入的研發費用則超過了8450億元人民幣。任正非明確表示,支持海思攀登珠峰,部分華為人將在山下種豆子等,并不斷送給登山人。在此情況下,華為將每年20%的營收作為資金支持海思,并承諾華為海思沒有盈利要求,不裁員、不重組,為海思招聘更多頂尖芯片人才。自去年底以來,華為海思半導體與器件業務部便開啟校園招聘工作,崗位涉及芯片與器件設計工程師、軟件開發工程師、硬件技術工程師、AI工程師、算法工程師等。

從華為將海思從二級部門獨立出來以及擴大人才儲備的動作來看,其不但沒有放棄海思,反而是進一步提高了在業務結構中的地位。

除此之外,一直備受關注的華為芯片設計問題也在發布會上得到了正式確認。

摩爾定律放緩,華為選擇芯片堆疊

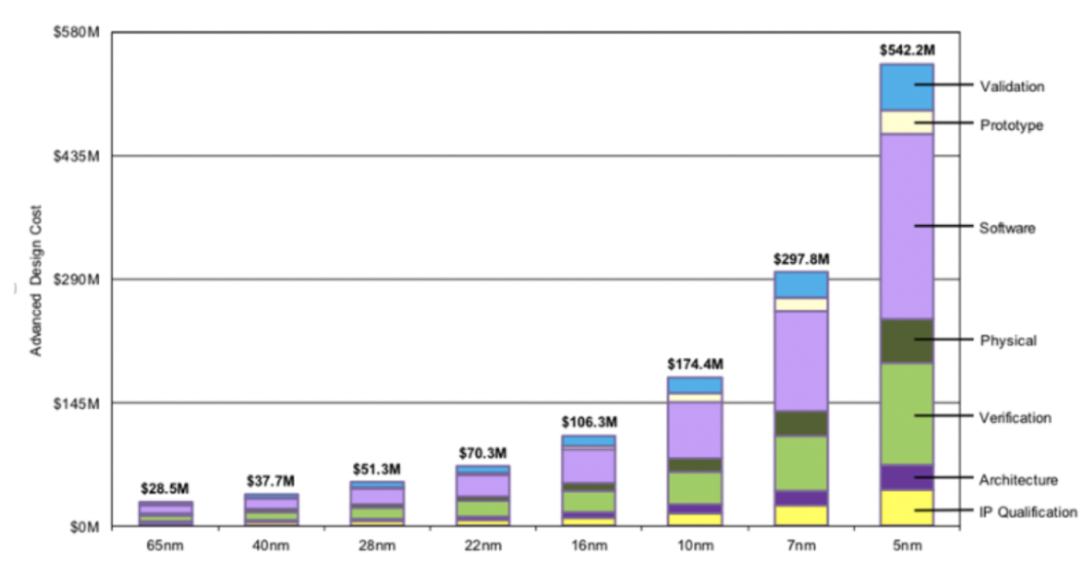

除了設計的高端芯片不能代工生產的問題以外,華為海思也面臨著另一個和全球其他廠商相同的問題,即芯片的性能受到摩爾定律的限制,先進制造工藝想要更進一步提升變得十分困難,高端芯片的設計成本也在大幅增加。據IBS數據顯示,設計一顆28nm芯片成本約為5000萬美元,而7nm芯片則需要3億美元,3nm的設計成本可能達到15億美元。

面對后一個問題,華為輪值董事長郭平在28日的發布會上表示,未來華為可能會采用多核結構的芯片設計方案,以提升芯片性能。同時,華為未來將用堆疊、面積換性能,用“不那么先進”的工藝來提升產品競爭力,這樣華為普通、成熟制程的芯片就有望重回舞臺。

蘋果在春季發布會上推出的1140億個晶體管的M1 Ultra芯片,采用的正是類似的技術:將兩塊晶體管數量為570億的 M1 Max 芯片堆疊到了一起,成功實現了性能的飛躍。

這種類似“膠水”的封裝大法,屬于Chiplet(小芯粒)的技術范疇,而國內最早嘗試Chiplet的正是華為海思。

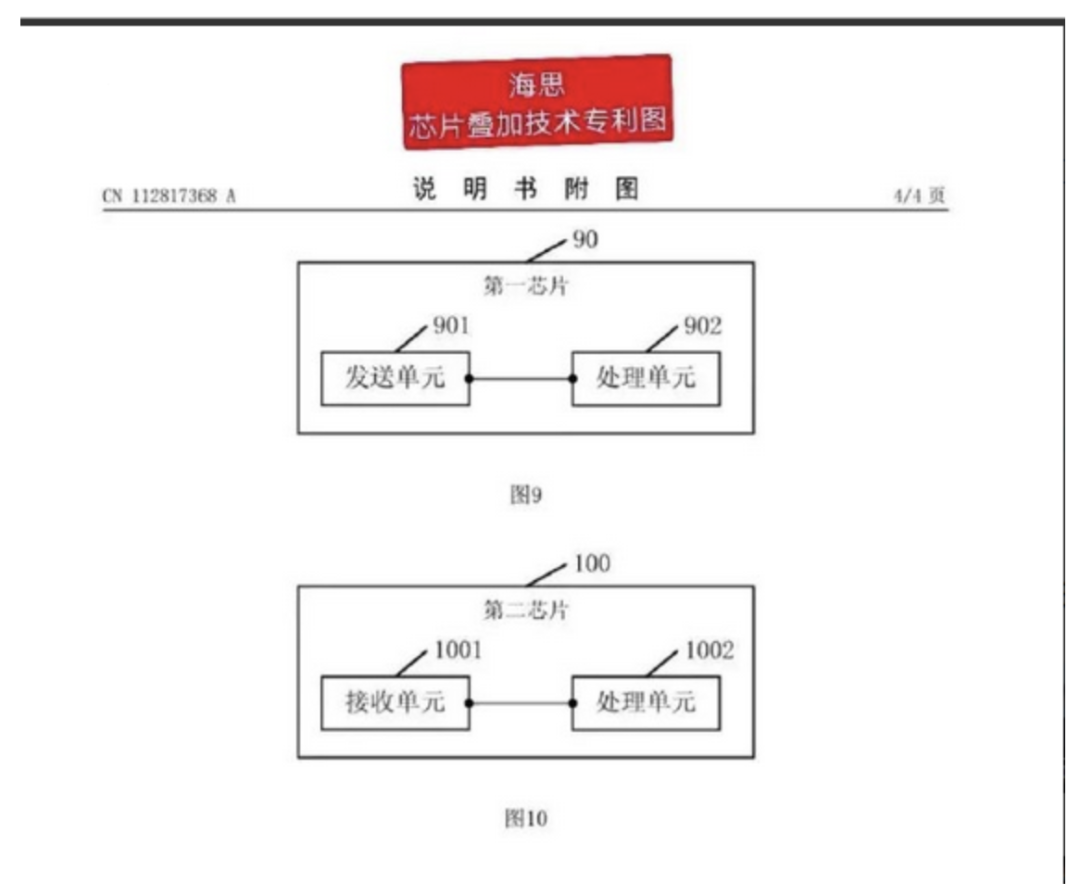

早在2014 年,海思就與臺積電合作過Chiplet技術。去年,網上又流傳出一份關于華為海思雙芯疊加的專利技術圖,闡述了將兩顆芯片疊加在一起組合使用的概念,還可能將利用3DMCM進行封裝。例如,可以通過特殊的設計,將兩顆14nm芯片疊加在一起,在性能上直接翻倍,堪比使用7nm技術。

在當時,這項專利并沒有引起過多的關注,甚至還有部分質疑的聲音表示:將兩杯50℃的水倒在一起,并不能達到100℃的效果。

但在今年3月2日,英特爾聯合10家芯片巨頭成立Chiplet標準聯盟,正式推出Chiplet的通用標準 “UCle”,用來打通各家芯片鏈接協議,構建一個開放可互操作的Chiplet生態系統。不過在這個聯盟中,既沒有華為的名字,也沒有任何大陸廠商參與其中,國內的芯片廠商似乎再次被針對。不過,這也從側面證明了華為的芯片堆疊技術是正確的方向,但在功耗方面可能會提高很多。

令人欣慰的是,有媒體報透露出國內Chiplet標準即將面世的消息,國標Chiplet草案已制訂完畢并有望在2022年第一季度公示,今年年底將進行《小芯片接口總線技術要求》初版標準發布,或將成為國產芯片打破制程封鎖,實現彎道超車的重要引擎。

寫在最后

進入2022年以來,隨著全球宏觀環境的急劇變化,很多國家和地區都在繼續加大對芯片的投入,如美國通過的520億美元的芯片法案和歐盟推出430歐元的芯片政策等。雖然有些技術是在重復開發,但是在如今的“逆全球化”背景之下,這些投資和研發也變得非常有價值。在現今工藝不可獲得,單點技術遇到困難的情況下,華為等企業一直在積極尋找系統的突破。

但是想要實現這一切都需要時間,沒有人可以給出準確答案,也許一兩年,也許更久,但只要能成功,這些都值得。

參考資料:

1.《華為加碼芯片研發:海思升格為一級部門》,C114通信網