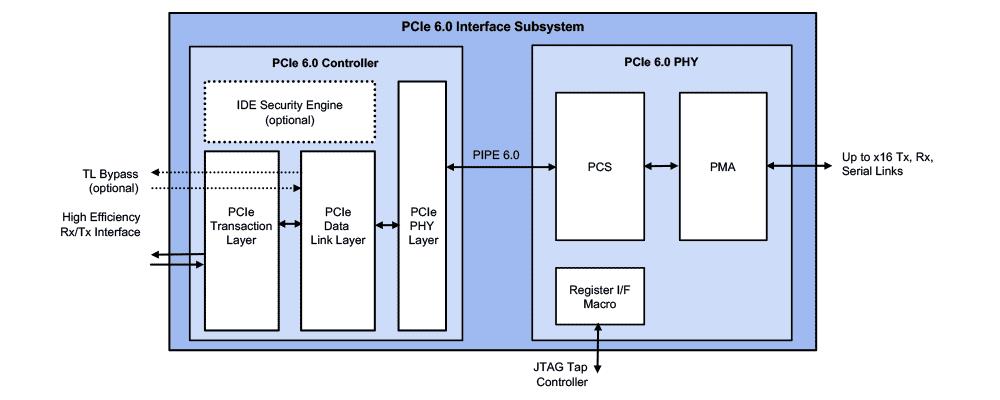

Rambus 剛剛發布了新一代 PCIe 6.0 接口子系統,旨在為下一代高性能數據中心和 AI SoC 解決方案提供鼎力支持。作為一家業內領先的芯片與硅 IP 供應商,Rambus 致力于讓數據更快、更安全。而今日隆重推出的 PCIe Express 6.0 PHY 和控制器 IP,還包含了對最新的 CXL 3.0 連接規范的支持。

(來自:Rambus Press Releases)

Rambus 接口 IP 總經理 Scott Houghton 表示:

人工智能(AI)/ 機器學習(ML)和數據密集型工作負載的快速發展,正在推動數據中心架構的持續發展,同時也對性能水平提出了更高的要求。

Rambus PCIe 6.0 接口子系統可滿足下一代數據中心所需的性能要求,且具有一流的延遲、功耗、面積和安全性。

規格方面,Rambus PCIe 6.0 接口子系統提供高達 64 GT/s 的數據速率,輔以滿足高級異構計算架構需求的全面優化。

在子系統內,PCIe 控制器具有完整性和數據加密(IDE)引擎,專用于保護 PCIe 鏈路和通過它們傳輸的有價值數據。

PHY 方面,它還提供了對 CXL 3.0 的全面支持,支持高速緩存、一致性內存共享、以及擴展和池化的芯片級解決方案。

其它 PCI Express 特性:

兼容 PCIe 6.0(64 GT/s)、5.0(32 GT/s)、4.0(16 GT/s)、3.1/3.0(8 GT/s)和 PIPE 6.x(8 / 16 / 32 / 64 / 128-bit)

支持 SerDes 架構的 PIPE 10b/20b/40b/80b 位寬

支持 original PIPE 8b/16b/32b/64b/128b 位寬

符合 PCI-SIG 的 Single-Root I/O 虛擬化(SR-IOV)規范

支持 FLIT / 非 FLIT 模式下的多個虛擬通道(VC)

支持端點(Endpoint)、根端口(Root-Port)、雙模(Dual-mode)、交換端口(Switch Port)配置

從 PCIe 6.0 向后支持到 PCIe 1.0 的速率

支持前向糾錯(FEC)-- 低延遲的輕量級算法

支持 L0p 低功耗模式

最高 4-bit 數據路徑奇偶校驗保護

支持時鐘門控和電源門控

RAS 功能 -- 包括 LTSSM 定時器覆蓋、ACK/NAK/Replay/UpdateFC 定時器覆蓋、未加擾的 PIPE 接口訪問、Rx 和 Tx 路徑上的錯誤注入、恢復詳細狀態等,允許在關鍵任務中安全可靠地部署 IP 系統芯片。

IDC 計算半導體研究副總裁 Shane Rau 表示:

PCI Express 在數據中心無處不在,而隨著公司追求不斷升級的速度和帶寬、以迎合下一代應用程序的更高性能水平需求,CXL 的重要性也在日漸提升。

此外隨著越來越多的芯片公司涌現、以支持新的數據中心架構,獲得高性能接口的 IP 解決方案、也將是啟用這一生態系統的關鍵。

最后,Rambus PCIe 6.0 接口子系統還具有如下主要特性:

支持 PCIe 6.0 規范,包括 64 GT/s 數據速率和 PAM4 信令。

通過部署低延遲前向糾錯(FEC)以提升鏈路穩健性

支持高帶寬效率的固定 FLIT 大小

向后兼容 PCIe 5.0、4.0 和 3.0/3.1